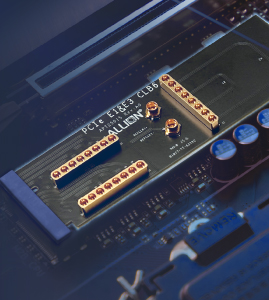

2019年5月,由PCI-SIG官方釋出了PCIe 5.0規範,傳輸速度為32.0GT/s,為PCIe 4.0的兩倍,其Throughput同樣分為 x1, x2, x4, x8, x16 Lanes,因此最高可以達到63GByte/s的傳輸能力,隨著傳輸效能提高,PCIe在消費性產品、Server或是工業領域等應用上,則扮演著更重要的角色。毫無疑問的,傳輸速度的提高也成為Connector的技術門檻,除了提高傳輸頻寬之外,Connector也不斷地縮小外型、提高密度以及致力於各方需求的整合。

Server是高頻應用中重要的領域之一,因應PCIe 5.0的時代來臨,Gen-Z、MCIO與SAS等Connector就顯得更為重要,本篇將先介紹Gen-Z和MCIO相關資訊,SAS Connector的細節則留在下一篇說明。

Gen-Z Connector

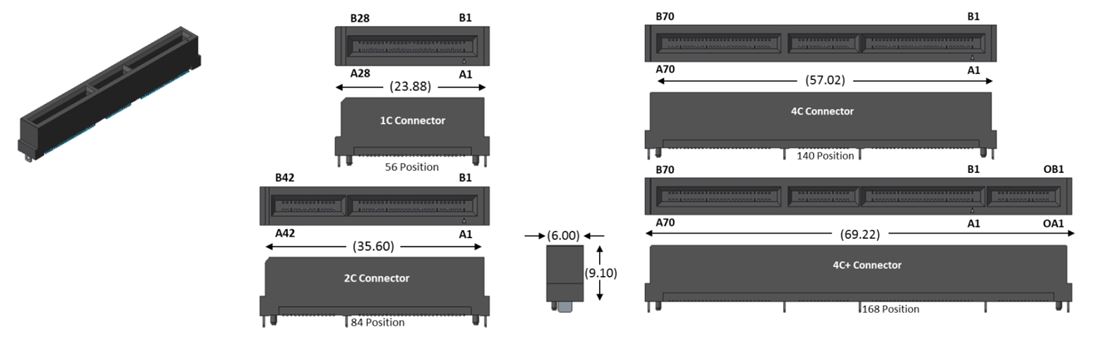

機構設計參考SFF-TA-1002的規範,分成1C、2C、4C、4C+四種Connector (如下圖),PCIe Pinout則參考SFF-TA-1009,而Gen Z的傳輸頻寬範圍則從2.5GT/s NRZ~112GT/s PAM-4,這樣的規格未來還可應用在PCIe 6.0。

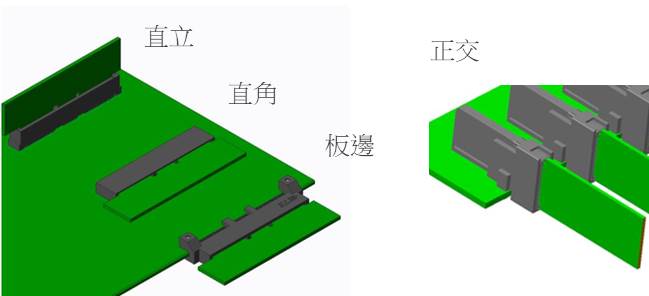

插槽方向如下圖,分成四種:直立(straight)、直角(right angle)、正交(orthogonal)、板邊(straddle),但須注意的是,正交方向插槽的傳輸頻寬最高為16GT/s NRZ。

Gen Z用於Server的Form Factor

DESFF E1.S

可以替代2,並且改善了過去M.2的一些缺點,例如:無法熱插拔、高溫與過溫。另外,PCIe在SSD的應用上預期最多使用4 Lanes(Gen Z, 1C) ,但以E1.S的Form Factor的設計條件,若有其他應用需求的話,Power可以提供到20W、8 Lanes(Gen Z, 2C)。

DESFF E3

用來取代2,PCIe的通道範圍從4 ~16 Lanes(Gen Z, 4C),Power最高可以到70W。

MCIO Connector

MCIO是什麼

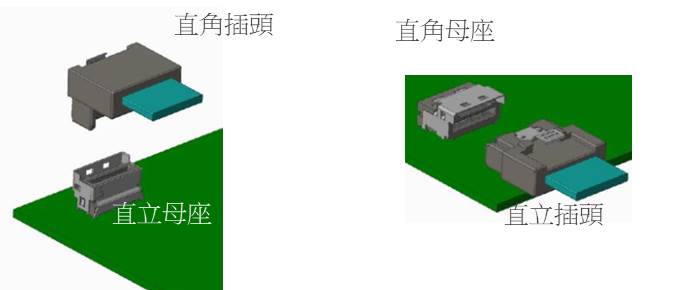

MCIO是Mini Cool Edge IO的縮寫,機構設計參考SFF-TA-1016規範,插槽如下圖分成直立(vertical)以及直角(right angle)兩種,Form Factor分成38pin、74pin、124pin以及 148pin,傳輸頻寬範圍則從25GT/s NRZ ~ 112GT/s PAM4,同樣未來也可被PCIe 6.0所擴充使用。

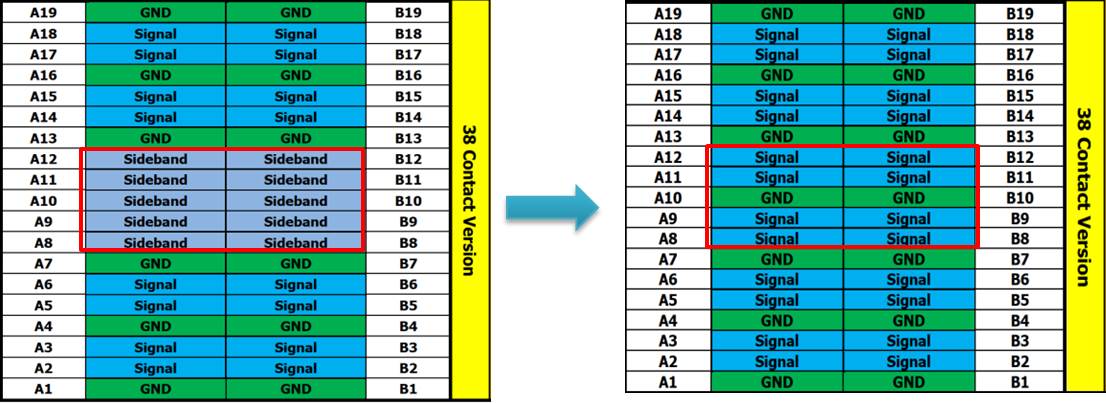

MCIO用pin數量來分類Form Factor而不用Lane的原因,是因為pinout定義中的sideband可以彈性作為高頻信號使用,以38pin的form factor來說明,原先定義的高頻pin只有x4 Lanes,但是將sideband作為高頻信號pin使用後,就可以擴充到x6 Lanes (如下圖)。因此PCIe的 x1, x2, x4, x8, x16 Lanes皆能符合其需求。

高速連接器的四大挑戰

如前面所言,傳輸速度提高的同時,Connector的pin size縮小、傳輸通道(Lane)的數量也隨之提高,比起過去低速的Connector來說是相對高的技術門檻。

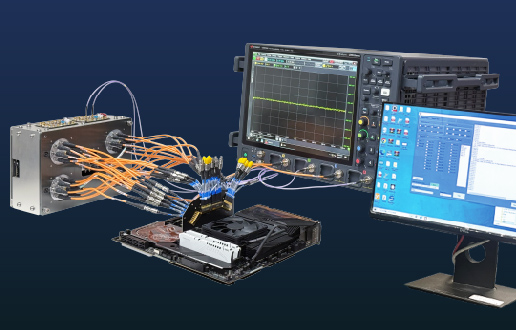

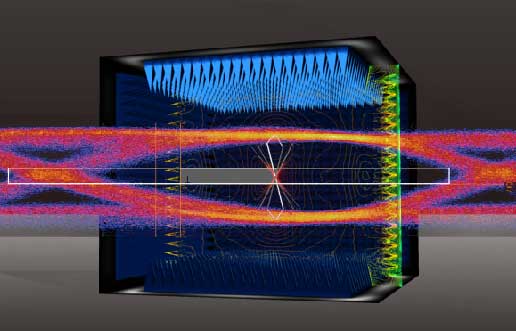

挑戰1:頻寬問題

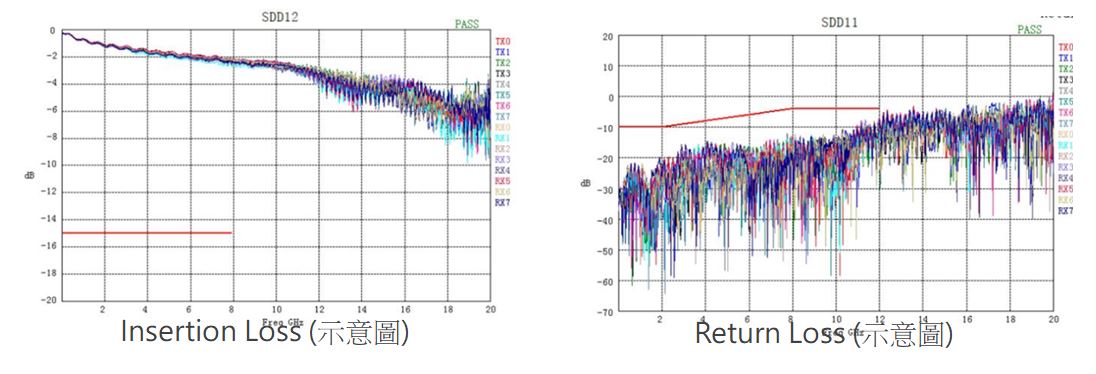

首先將面臨的是頻寬問題,是否能達到傳輸期待的速度?頻寬的好壞由Insertion Loss (IL)和 Return Loss (RL)決定,與金屬的材質、厚度、寬度、都有直接與間接的關係。

理想上都是 IL與RL都是越小越好(損失小),也代表傳輸資料頻寬能夠上升。

挑戰2:接觸阻抗

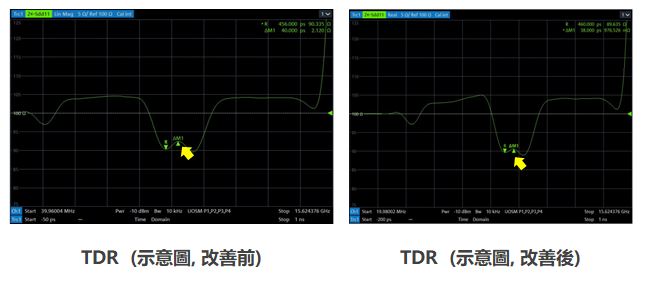

第二個挑戰則是Plug與Receptacle接觸時的接觸阻抗(並非接觸電阻)。接觸阻抗太差,當遇到較高頻的信號時會產生極大的return Loss,導致頻寬下降。

挑戰3:串音干擾

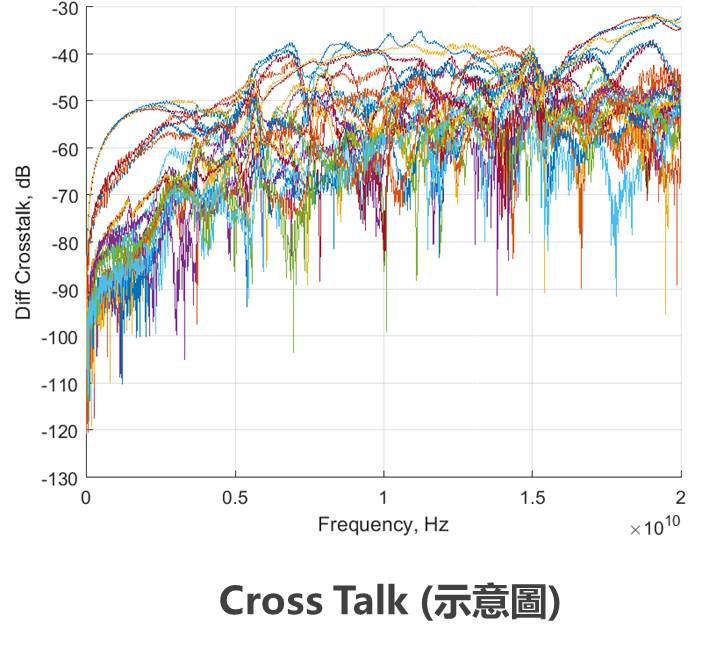

第三個挑戰則是串音(Crosstalk),剛剛提到pin size縮小、Lane數量提高,導致高速pin之間靠得更近,這些條件都會提高crosstalk影響。另外,信號的radiation太強(例如return loss太大所造成)也會提高crosstalk。

挑戰4:傳遞時間差 (Skew)

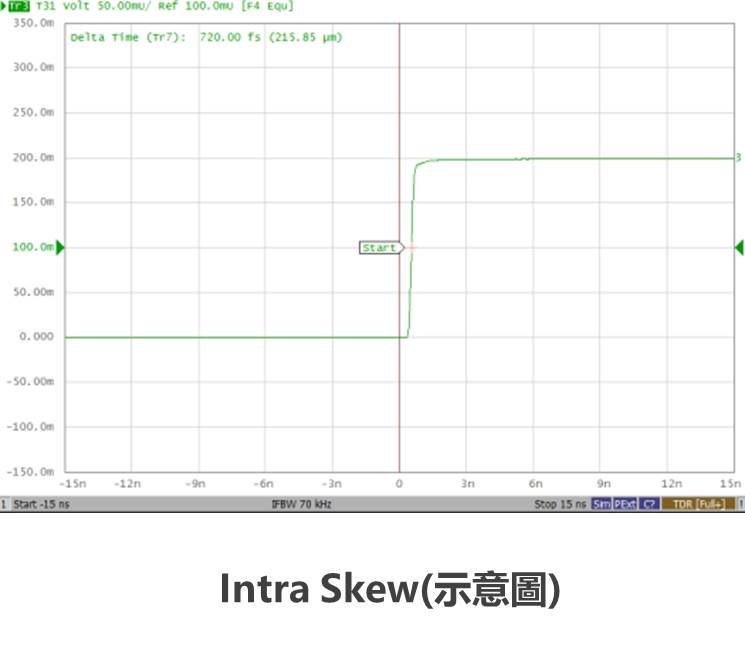

最後的挑戰則是Skew,指的是兩個相同信號同時進入connector,量測輸出信號之間的時間差,低頻的時候兩者信號差個數十ps或許不會有錯誤發生;但是當在高頻的時候,5~10ps的時間差就極有可能發生錯誤。高頻pin與pin之間的skew稱為intra skew,而高頻對線之間(pair與pair之間),稱之為inter skew,因此,要能讓每pin的信號誤差都在規範內,也成為一大挑戰。

以上介紹了Gen Z與MCIO connector以及面臨高速信號的挑戰。百佳泰為各標準協會(ex. USB, HDMI, DisplayPort…)所認證的Cable & Connector ATC (Authorized Test Center),對於高頻信號的線材及連接器有30年實驗室、驗證測試等豐富經驗。

想了解百佳泰更多伺服器相關服務內容,請點選:https://www.allion.com.tw/server-validation/

如欲諮詢協助,歡迎隨時聯繫我們:service@allion.com