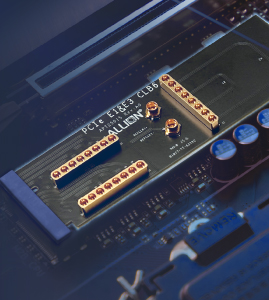

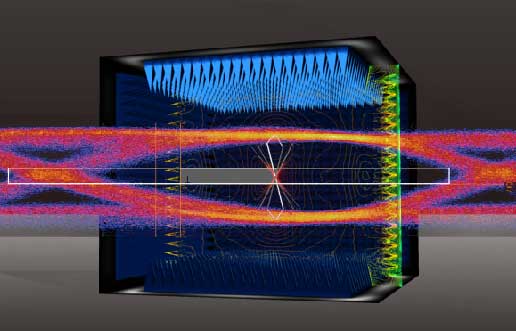

自從AI伺服器、GPU加速卡、NVMe SSD、工業電腦、高階主機板與交換器平台快速演進,PCIe早已不只是介面名稱,而是牽動整體系統效能、穩定性與相容性的關鍵樞紐。不管是通道速率持續提升、板材與走線設計日益緊湊,或是異質整合與Retimer/Redriver元件導入成為常態,這些變化正全面翻轉PCIe電氣特性驗證的角色定位。百佳泰以關鍵工程化流程 ,將高速介面導入的挑戰化解,將量測結果成為可交付、可溝通的工程證據!

PCIe應用困局與導入風險有哪些?

多數客戶在專案中最核心的需求

不是測不到!而是「難以確定測得對」

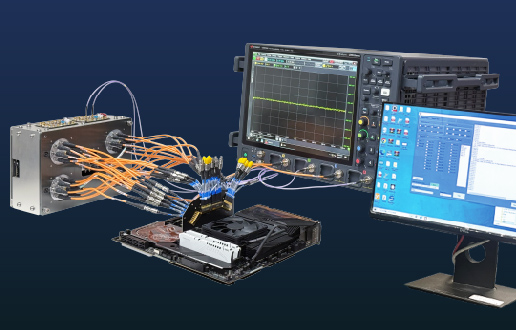

在PCIe這類高速差分介面上,真正的痛點時常不是「是否執行過測試」,而是以下的實務難題:

- 內部資源與設備門檻高

高速電氣量測牽涉高頻示波器、探頭/探棒、治具設計、校正流程與工程經驗,前期投資與長期維護成本高。 - 量測結果難以重現與比較

不同治具、校正方式與測試條件,往往造成「數據看似接近,但結論差異大」,導致內部難以形成一致判斷。 - 跨團隊溝通成本高

硬體、SI/PI、韌體與系統整合團隊各自解讀數據,若缺乏一套可追溯的測試計畫與報告架構,問題往往難以快速收斂。 - 終端客戶與品牌商要求日趨嚴格

客戶不再只接受pass/fail結果,而是要求清楚的量測條件、測點定義、裕量分析與第三方驗證背書。

這意味著許多專案常常卡在「產品已接近完成,但驗證證據不足」的關卡,後續不是被迫延遲出貨,就是帶著不確定性進入量產,導致可能後續再以更高成本補救。

應用工程化流程 交付PCIe電氣特性測試與可用結論

如果你還在覺得百佳泰的PCIe電氣特性測試的價值僅在單次量測,那你就錯了。來看看百佳泰如何協物將測試轉化為可交付、可追溯、可溝通的具體工程成果:

測試規劃

依產品形態(Add-in Card、主機板、背板、Cable、Retimer/Redriver)與客戶驗收需求,定義測項、測點、測試條件、樣品與批次策略,並建立風險優先序。

第三方測試報告

以第三方立場提供完整報告,涵蓋量測設定、校正方法、波形結果、裕量分析與判讀依據,作為對外驗證與稽核依據。

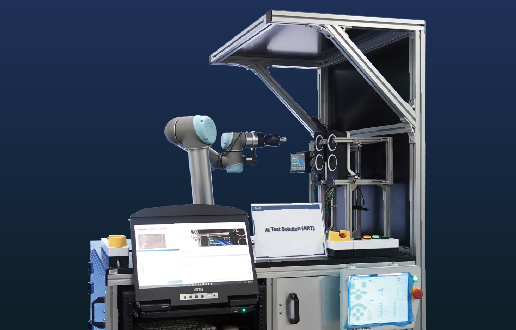

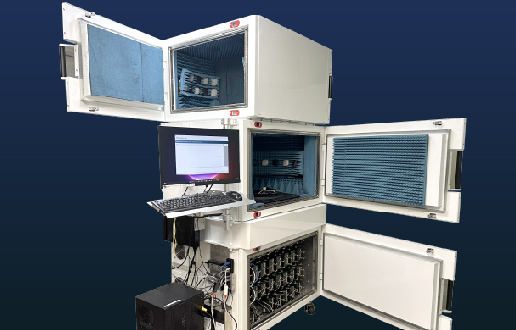

量測治具與校正機制

- 在PCI-SIG僅針對標準CEM形態定義官方量測治具的情況下,百佳泰已依實際產品應用需求,自行開發並累積多種非CEM形態之量測治具,涵蓋OCP NIC、EDSFF E1 與 E3、2、U.2等常見高速介面與儲存模組形態,並且可針對實際走線、連接器與系統結構協助客製化治具。

- 治具設計皆納入完整的校正流程與誤差控制機制,以提升量測結果在不同產品形態與平台間的可重現性與可比較性,並可支援最新PCIe 6.0規格,適用於多元高速產品應用情境。

問題現象分析與除錯支援

除提供量測數據與測試結果說明外,亦協助問題現象的初步分析,並依量測觀察結果提出可能的設計、佈局、材料或參數調整方向,供客戶於後續設計與驗證階段參考,以協助測試結果與實際設計決策之銜接。

給正在打造高速平台的你:與其賭「應該沒問題」,不如用數據提前把關

PCIe的問題往往不是「完全不能用」,最可怕的是只在特定負載、溫度或平台條件下才會浮現。因此,越早以正確的方法收斂不確定性,越能將成本控制在研發階段。

若你正面臨驗證時程緊迫、內部設備與人力不足、客戶要求第三方測試報告,或需要治具與測試計畫支援,百佳泰可依你的產品形態與交付目標,提供對應的PCIe電氣特性測試方案與報告交付,協助你把高速設計化背後的風險,確實留在實驗室。

有煩惱,就來問!百佳泰專家幫你解答

不論產品、產業、生態圈,填表就能問專家!

更多成功案例