實際案例說明

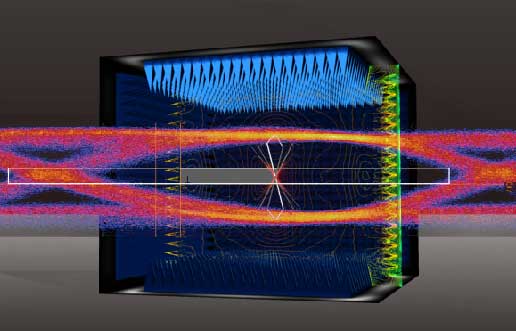

客戶為高效能平台開發廠商,於新一代平台進行DDR4 electrical validation,除既有的DRAM side合規量測需求外,進一步希望同步掌握CPU side DDR訊號品質表現,藉由雙端點量測,從系統角度評估整體通道設計是否具備足夠的設計裕量,作為後續參數調校與風險評估的重要依據。

客戶需求與實務挑戰

由於該平台在設計初期未針對DDR高速訊號預留DRAM side量測點位,使得後續驗證階段無法直接依循JEDEC規範進行標準電氣量測。因此即使客戶具備完整的量測設備與測試能力,仍因量測介面受限,難以取得具代表性且可用於合規判定的數據,成為驗證流程中的首要瓶頸。

並非單一端點是否通過規範測試,而是希望從整體系統角度,全面掌握DDR記憶體通道的實際訊號品質表現,包括:

- 同步比較DRAM side與CPU side在DDR4電氣行為上的差異

- 釐清是否因通道走線、封裝效應或SoC PHY設計因素,導致timing margin被壓縮

- 將量測觀察轉化為可行的系統設計回饋,支援後續的參數調校策略,如 read/write leveling 與ODT設定最佳化

- 實務執行上,CPU side量測受限於探棒接觸空間不足、波形擷取困難

- 量測結果與 JEDEC 規範之間不易直接對應,使內部團隊在驗證策略規劃與數據解讀上承受相當壓力。

百佳泰顧問團隊以顧問式驗證流程,協助客戶整合DRAM side與CPU side的量測結果,將數據轉化為可回饋至系統設計的實務判斷。

解決方案:規範導向 × 系統觀點的整合驗證策略

針對上述需求,百佳泰顧問服務團隊導入「規範導向分析 × 系統層級解讀」的驗證流程,協助客戶建立可落實的驗證架構。

-

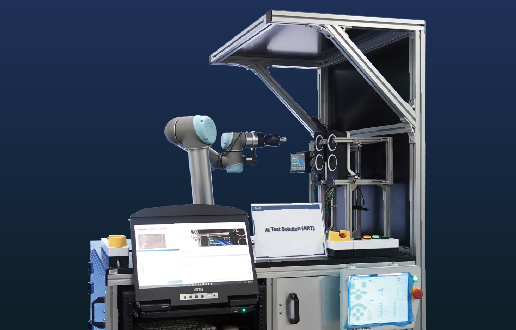

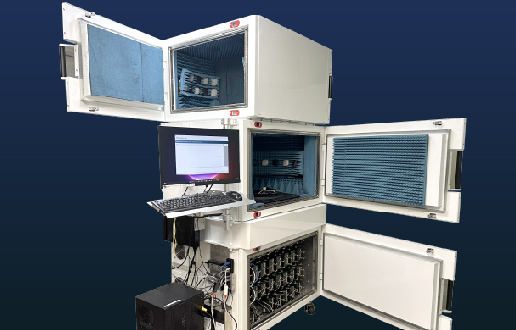

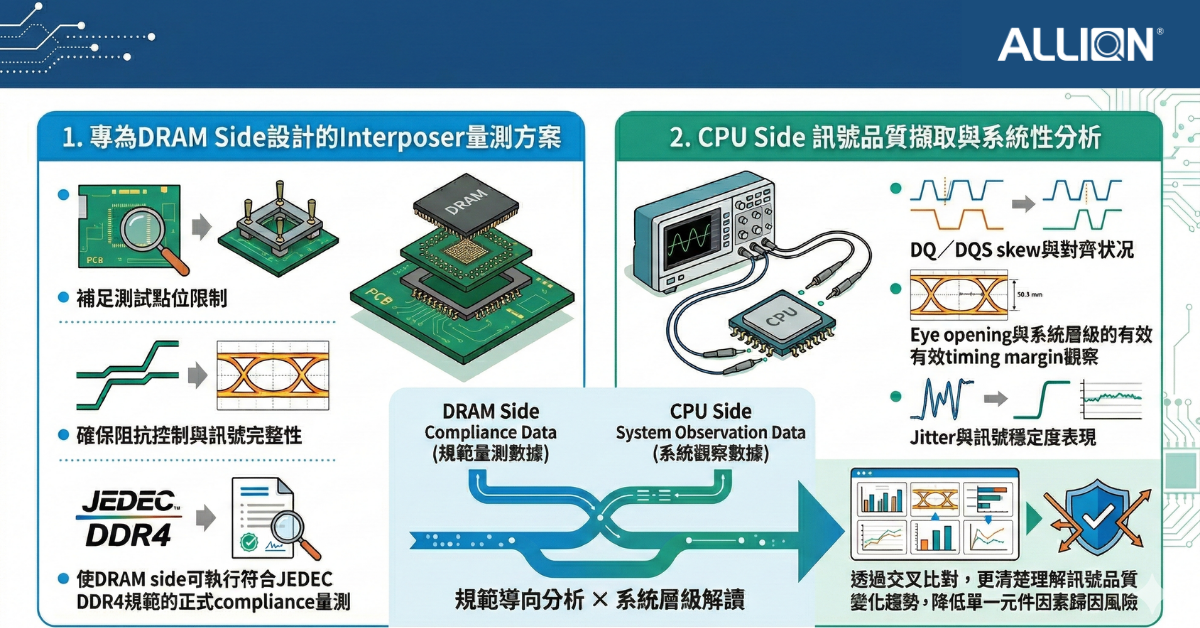

專為DRAM Side設計的Interposer量測方案

憑藉多年高速治具設計與記憶體量測經驗,百佳泰為客戶量身設計DRAM量測治具(Interposer / Spacer Board):

- 補足平台缺乏測試點位的限制

- 確保阻抗控制與訊號完整性

- 使DRAM side可執行符合JEDEC DDR4規範的正式compliance量測

-

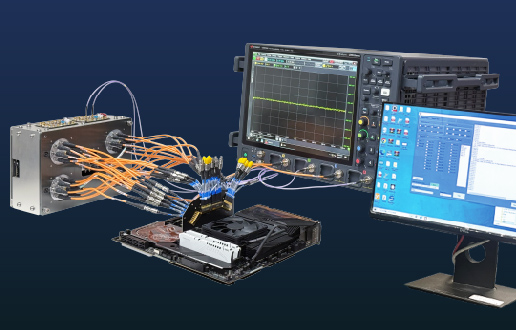

CPU Side 訊號品質擷取與系統性分析

在完成DRAM side規範量測的同時,依客戶需求於CPU side擷取對應的DQ/DQS波形,使用高頻寬示波器與低負載差動探棒進行分析,重點包含:

- DQ/DQS skew與對齊狀況

- Eye opening與系統層級的有效 timing margin觀察

- Jitter與訊號穩定度表現

CPU side量測並非用於JEDEC規範判定,而是作為系統內部相對比較與通道行為觀察之用。透過與 DRAM side 規範量測結果進行交叉比對,可更清楚理解訊號品質在通道中的變化趨勢,並降低將系統性問題過度歸因於單一元件或製程因素的風險。

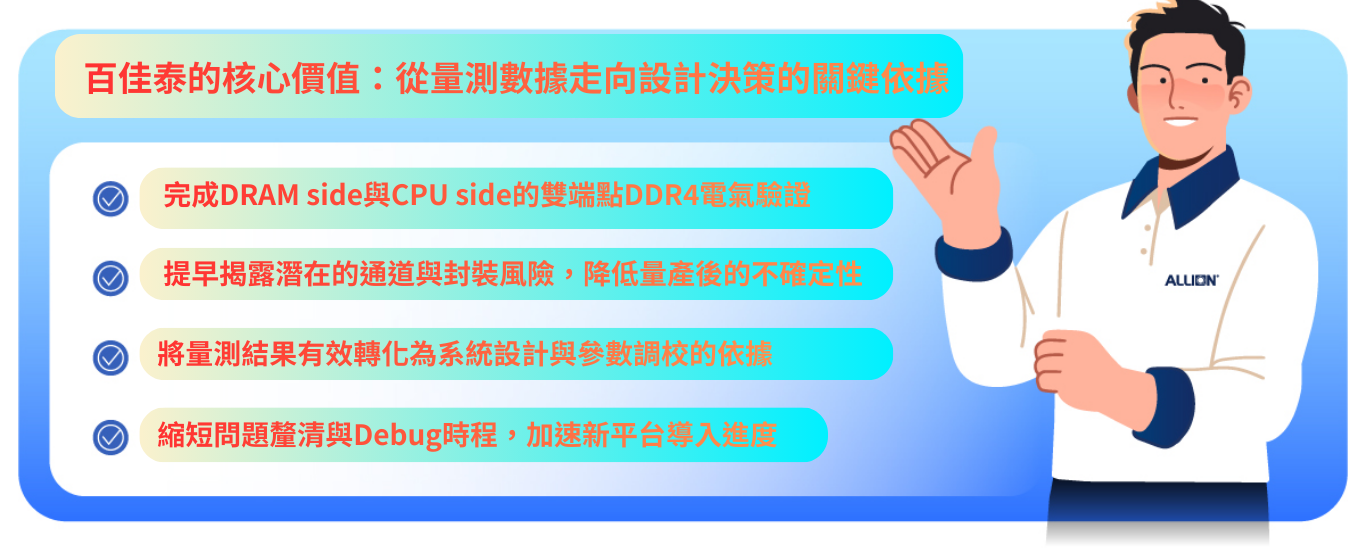

百佳泰的核心價值:從量測數據走向設計決策的關鍵依據

透過本次整合驗證專案,百佳泰協助客戶:

DDR驗證不只是「合規」,而是「可用且穩定」

在高速記憶體設計中,真正的挑戰不在於是否符合規範,而在於系統是否具備足夠的設計裕量與長期穩定性。透過結合標準化量測、專用治具與系統層級分析,百佳泰協助客戶從單點驗證走向整體通道理解,讓DDR電氣驗證成為可支撐設計決策的關鍵工具。未來,百佳泰也將持續以專業量測能力與顧問式驗證經驗,成為高效能運算與伺服器平台在高速記憶體設計領域中,值得信賴的長期技術夥伴。

線上表單