PCIe® Gen 5 到PCIe Gen 6 可以說是一次極具指標性的重大技術飛躍,尤其是在訊號傳輸和編碼方式上有著許多更新。在今天的文章中,百佳泰將透過實際量測與深度解折,帶你一次看懂其箇中差異!

PCIe Gen 6 與PCIe Gen 5的五大主要差異

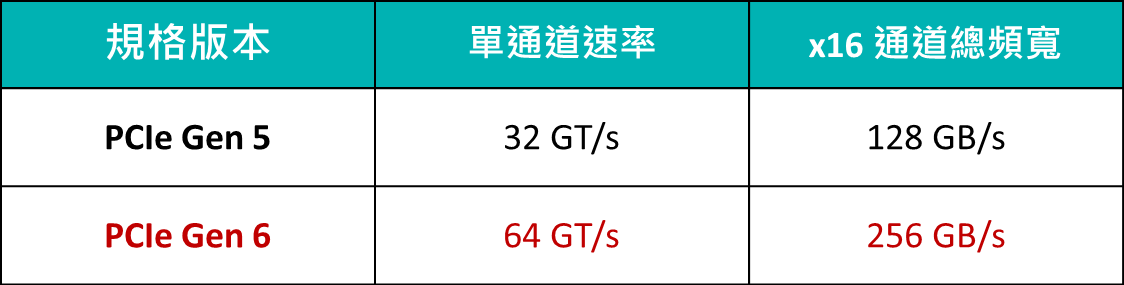

傳輸速率與頻寬

Gen 6 的速率是 Gen 5 的兩倍,相當適合 AI、HPC、高速儲存等高頻寬應用。

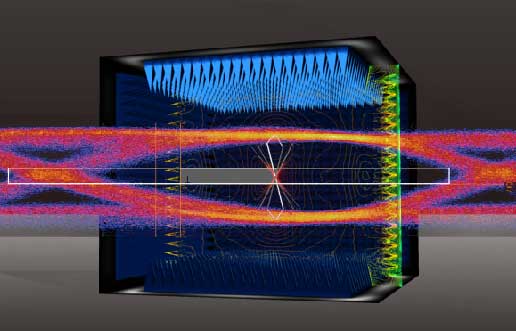

訊號調變技術

Gen 5 使用 NRZ(Non-Return to Zero)兩電平訊號。Gen 6 則改用 PAM4(Pulse Amplitude Modulation 4)四電平訊號,雖然能在相同頻率下傳輸更多資料,但同時也帶來更高的誤碼率。

編碼方式與錯誤修正

Gen 5 採用 128b/130b 編碼。Gen 6 則改為 FLIT(Fixed-Length Transaction)編碼,並引入 FEC(前向錯誤修正)與 CRC(循環冗餘檢查)來降低 PAM4 的誤碼率。

功耗與新功能

Gen 6 增加了 L0p 低功耗狀態,允許部分通道進入 idle 模式以節省能耗。除此之外,Gen 6也新增了像是DOE、CMA、DMWr、IDE 等機制,有助於提升安全性與資料傳輸效率。

向下相容性

Gen 6 保持與前代 PCIe 裝置的相容性,讓升級更具彈性。

在技術不斷演進的浪潮中,產品的更新換代不僅反映了創新思維的推進,也揭示了市場需求的深層變化。接下來我們將聚焦於不同版本與世代的產品演化,一一剖析它們在設計理念、性能表現、以及在各種應用場景上的差異與升級。希望能夠藉由這樣的版本直接對照,幫助大家能夠更清晰地理解各世代技術的優勢與侷限,進而挑選出符合需求的解決方案。

緊接著,百佳泰將深入比較兩代產品在以下面向的差異:

- Impedance的差異(PCIe Gen 5.0)

- Insertion Loss @16GHz

在開始測試之前,我們還是先針對Gen 6 快速地科普一下。

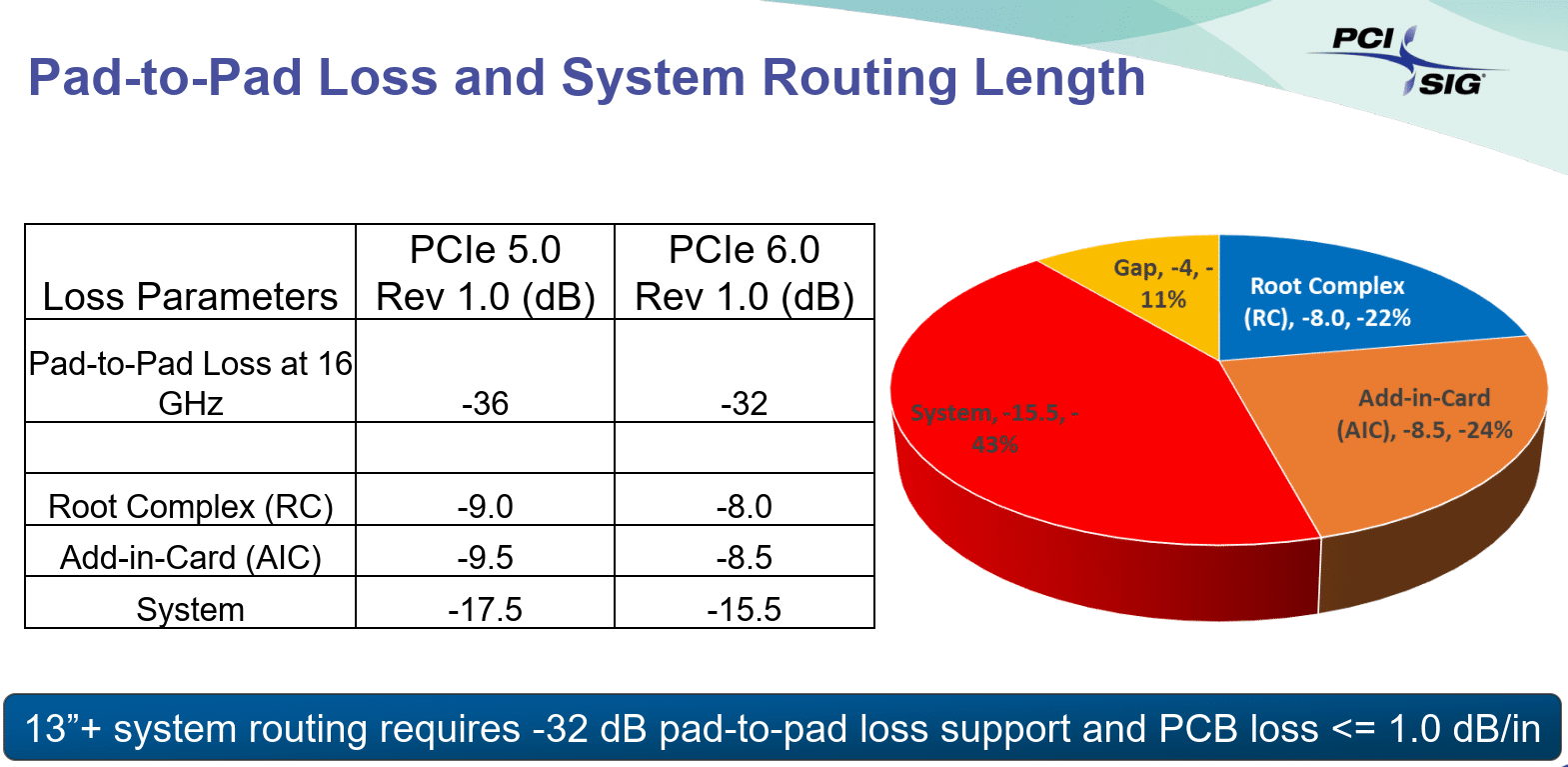

- Loss Budget:從 36 dB 變成 32 dB。

- Add-in Card Insertion Loss Budget:從 9.5dB 變成 8.5dB。

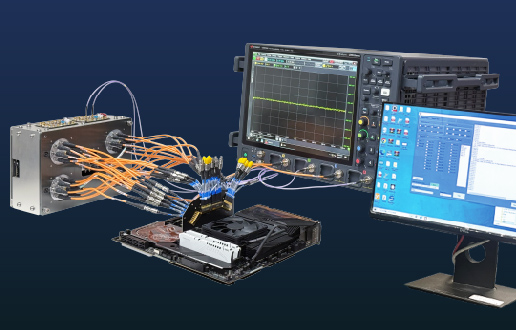

在測試設定上,我們使用的儀器是R&S 67GHz VNA

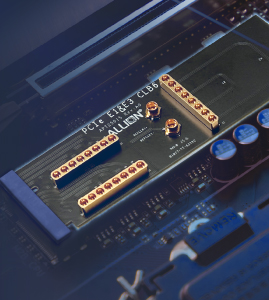

PCIe Gen6 CLB + PCIe Gen6 CBB

Impedance Measure Setting

- Rise Time:23.125ps

- Rise Time Definition:10%~90%

Insertion Loss Setting

- Start Frequency Range:10MHz

- Stop Frequency Range:40GHz

- Look at 16GHz/24.5GHz/36GHz

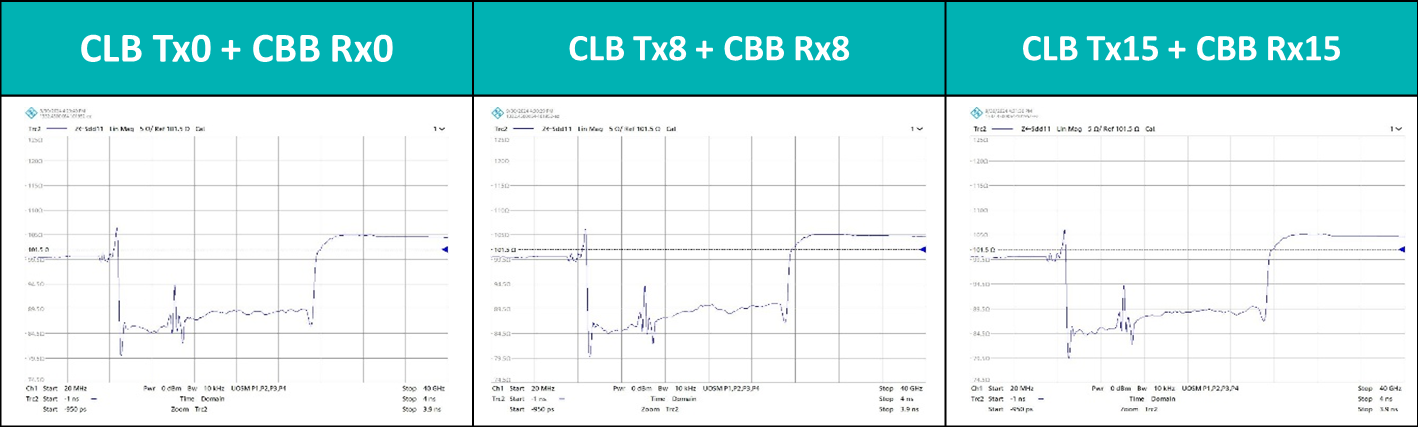

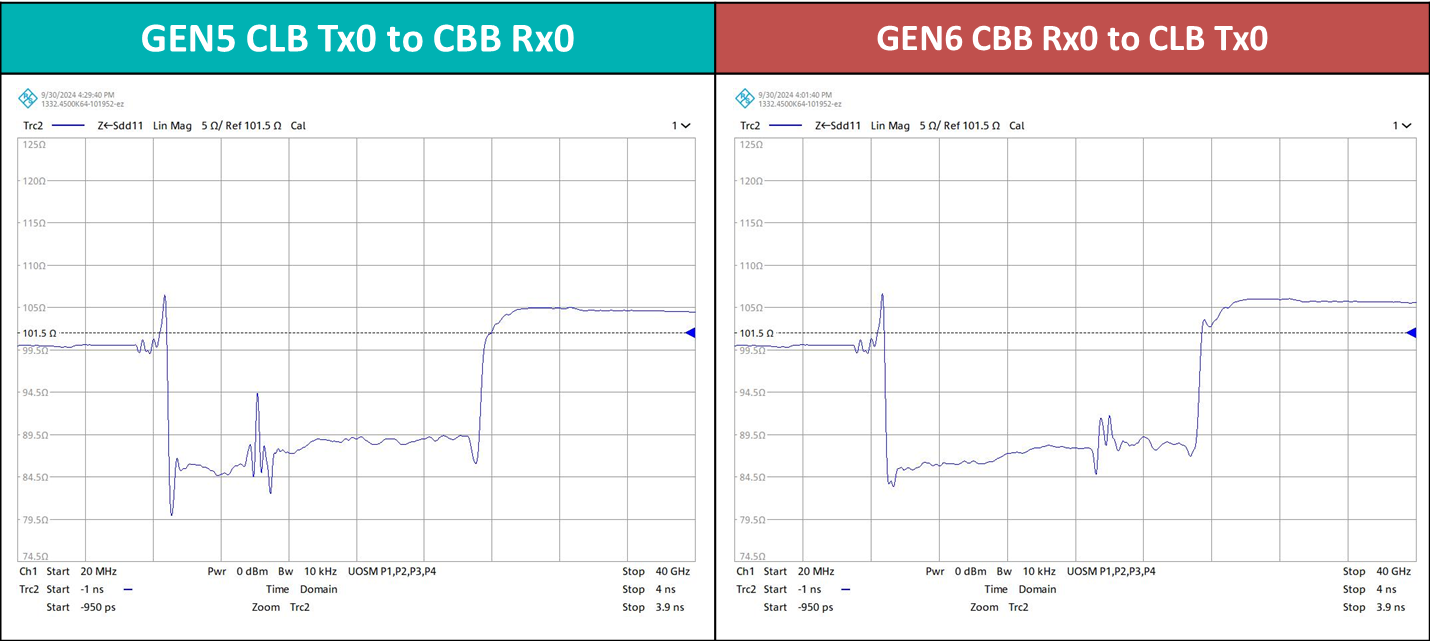

如果不是因為PCB色澤上的差異以及字面標示的不同,我們其實很難單從外觀上辨別兩者之間的差異。(特別是所有的零件位置和佈局幾乎是完全一模一樣)。由於協會治具採用MMPX 設計,以致於出現CLB Tx(約莫2”)信號較短而Rx信號較長(約莫3~4”)的差異,但是在CBB Tx & Rx 的信號卻又是等長(約莫3~4”),所以在對接之後會反應出不同的Impedance & Insertion Loos 的表現,於是我們採用短中長三對來呈現出測試的共通性和一致性。

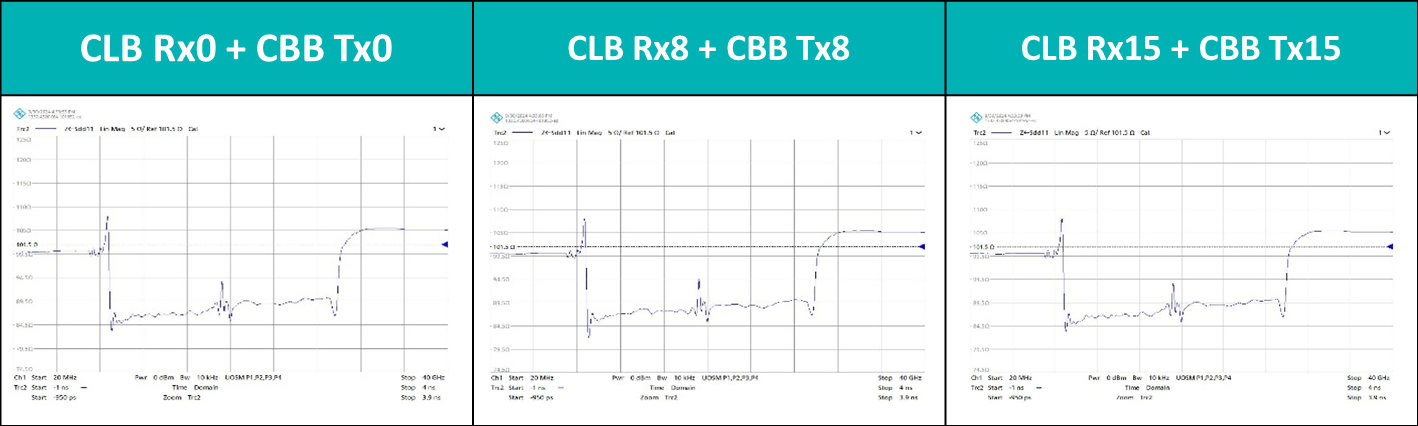

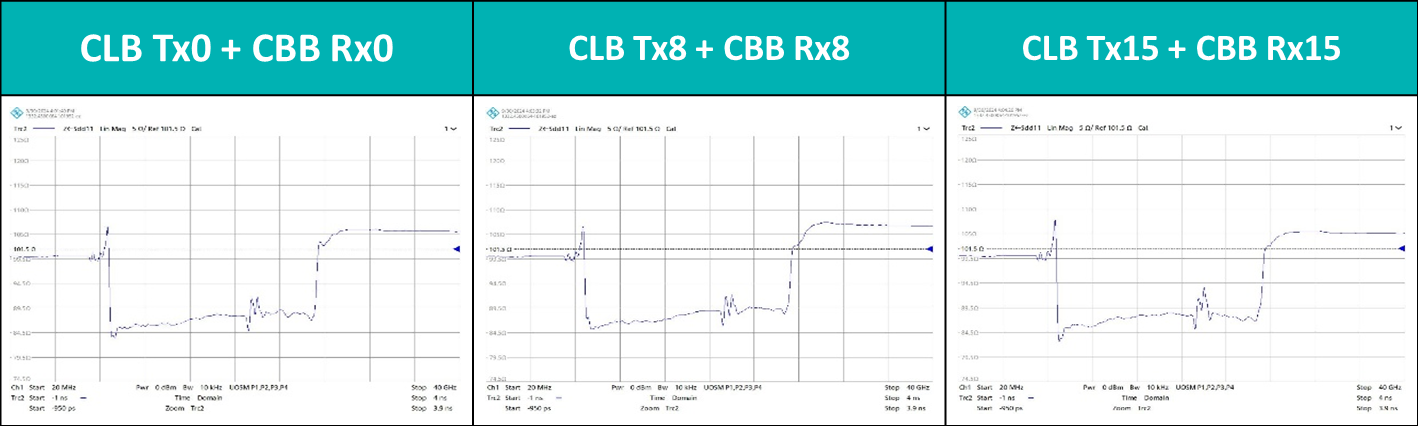

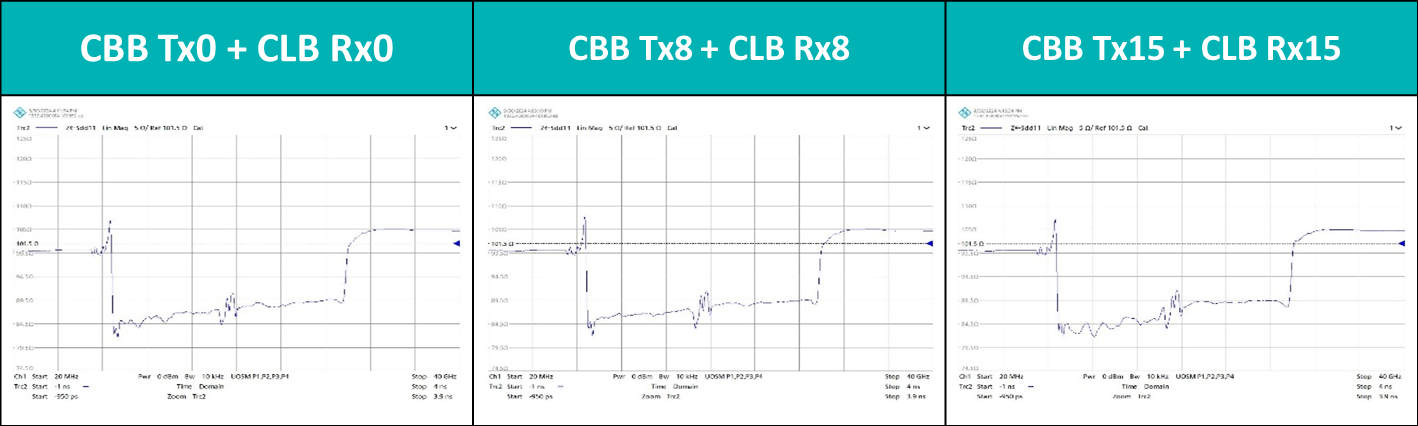

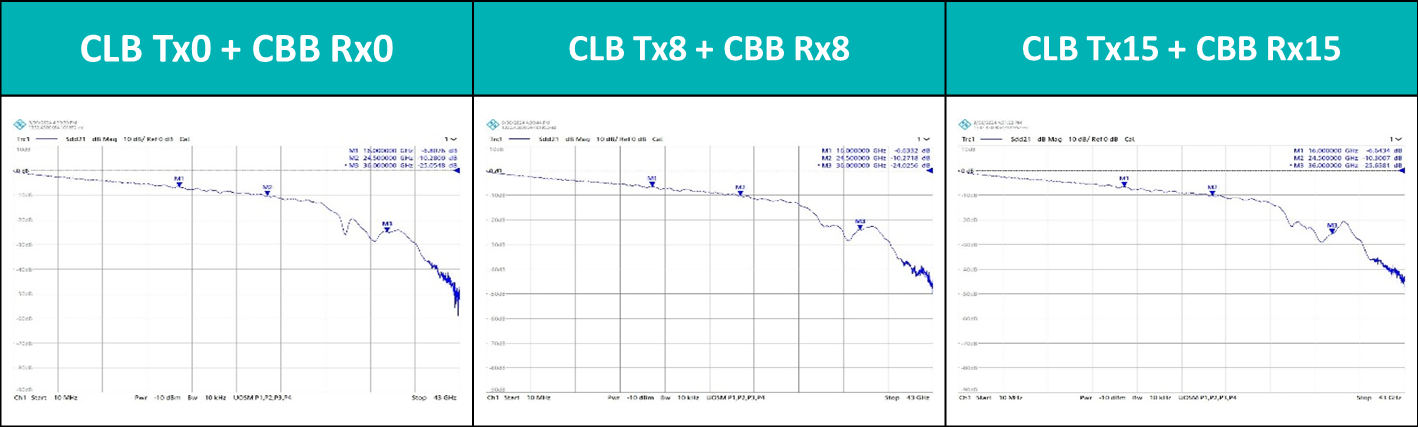

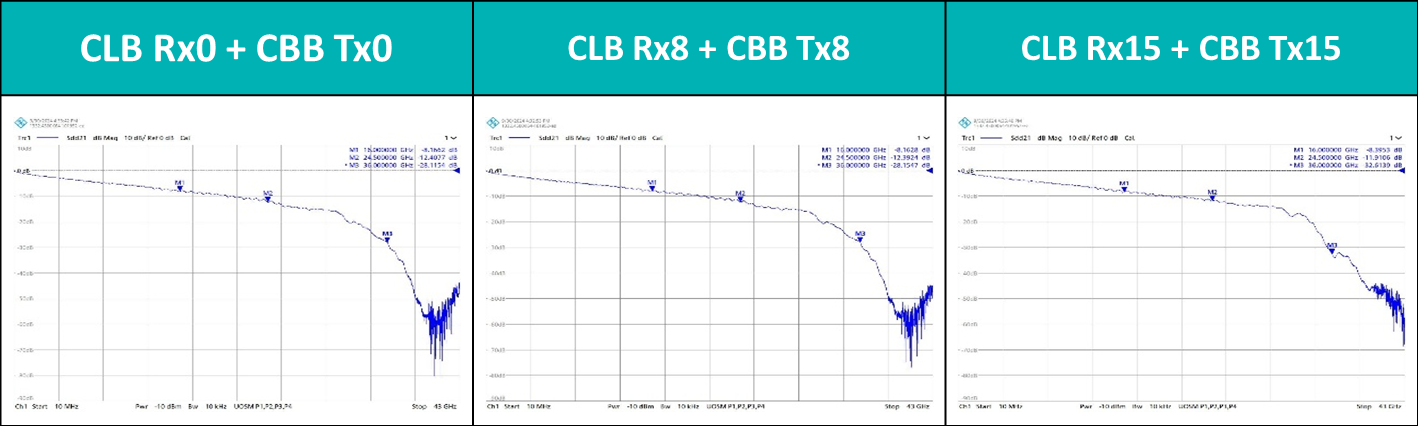

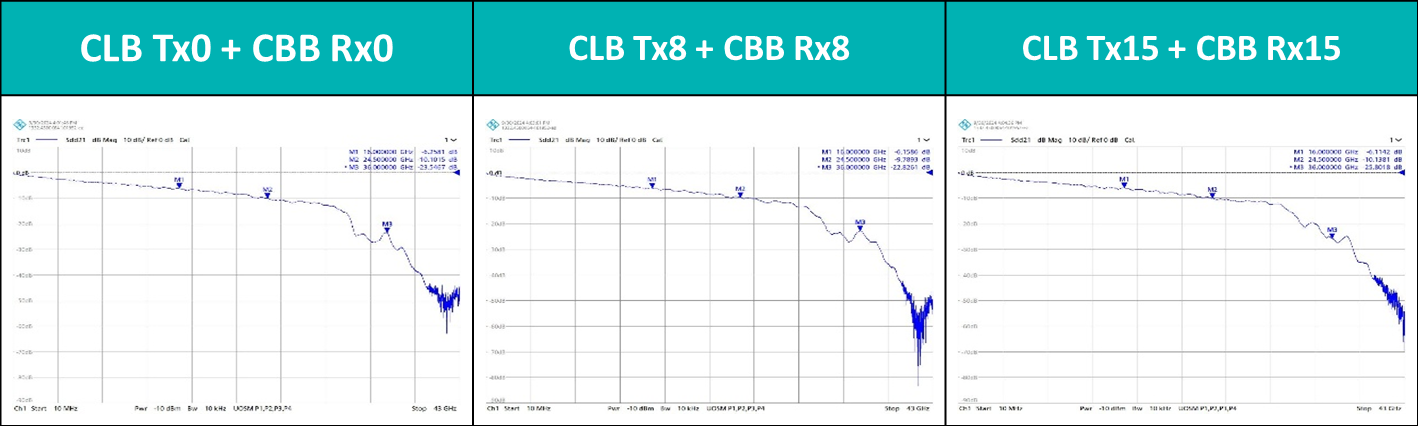

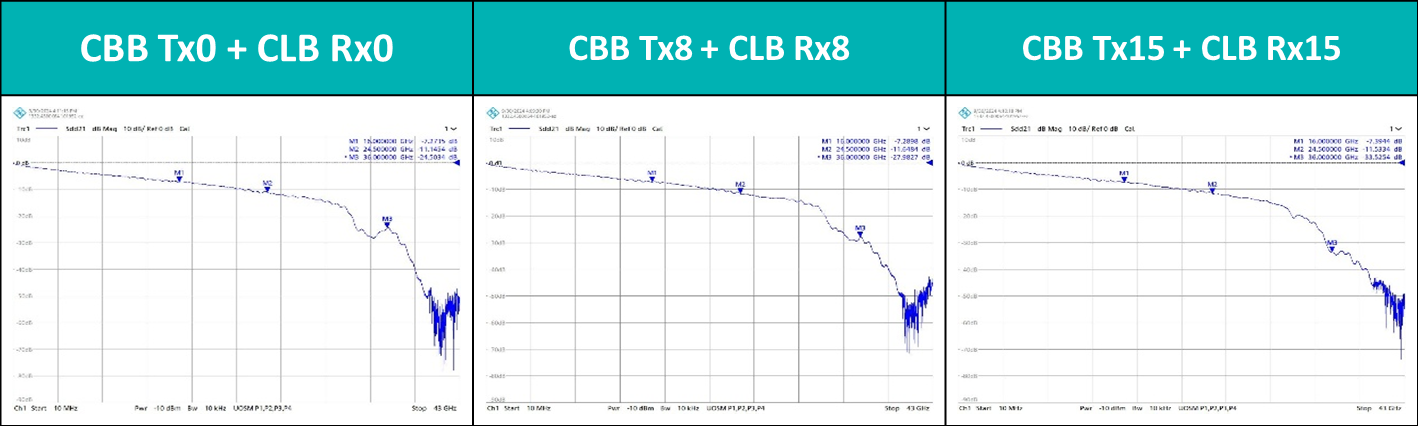

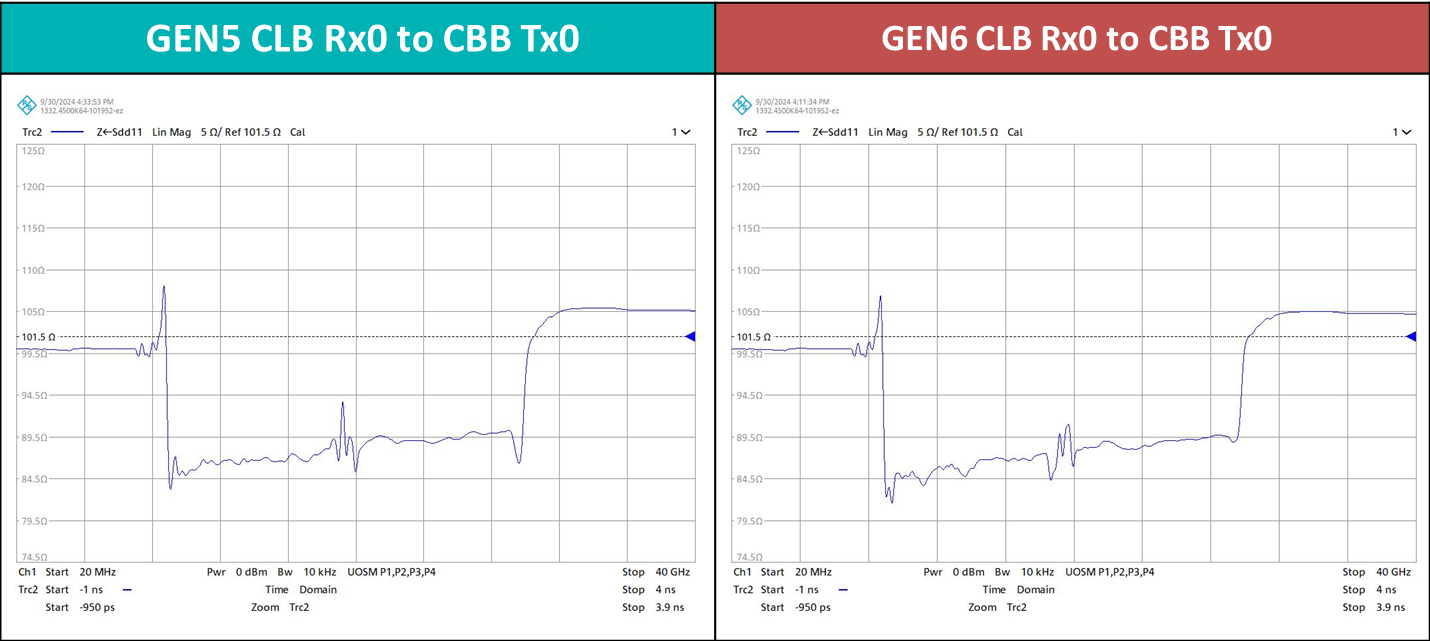

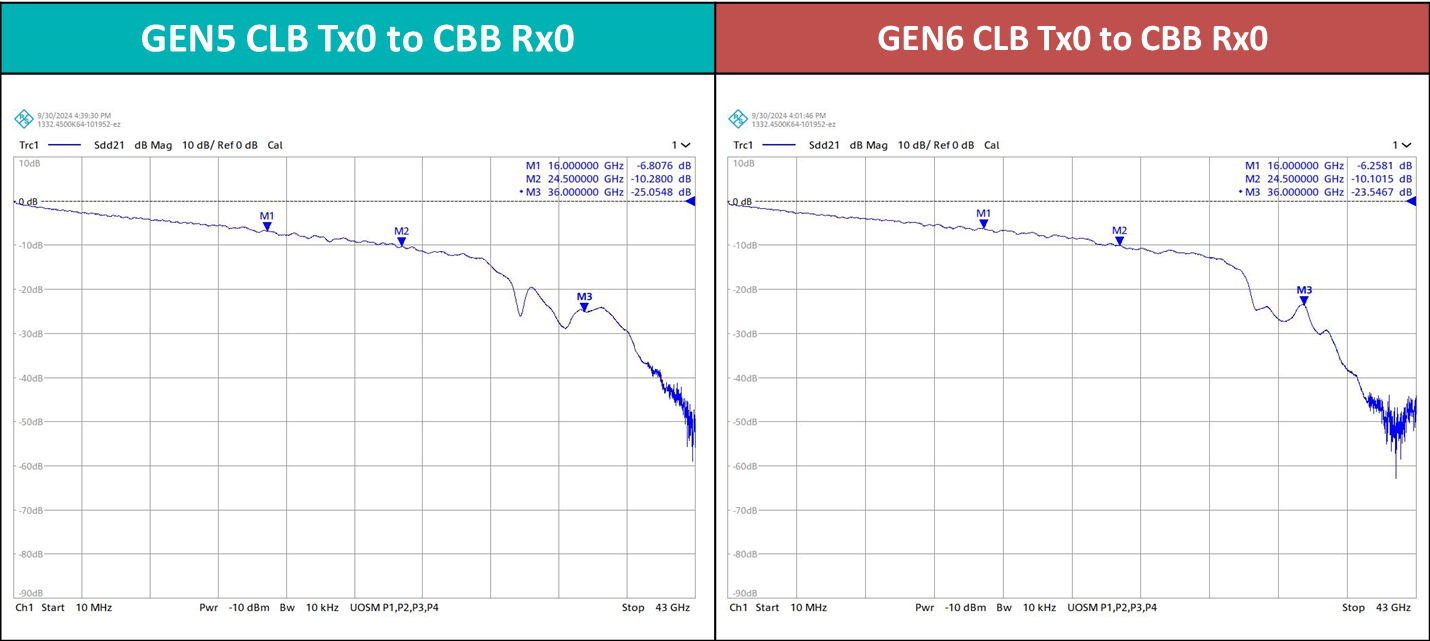

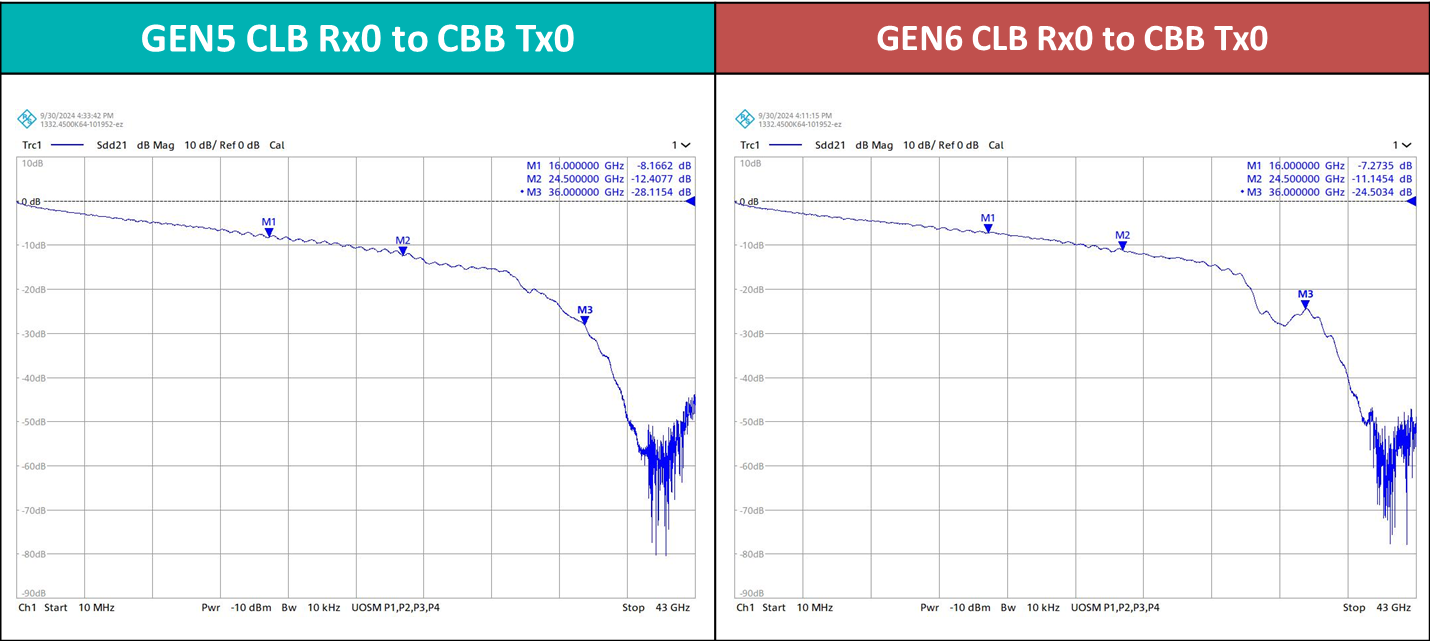

在測試中,我們使用CLB Tx0/Tx8/Tx15 對應 CBB Rx0/Rx8/Rx15,以及 CLB Rx0/Rx8/Rx15 對應 CBB Tx0/Tx8/Tx15,來探究之間的差異。

接下來就來呈現我們所量測出來的結果:

1. Impedance

PCIe CEM Gen5 CLB

PCIe CEM Gen6 CLB

2. Insertion Loss@16GHz,

PCIe CEM Gen5 CLB

PCIe CEM Gen6 CLB

根據上面Gen5 和 Gen6的測試結果,以下讓我們簡易的整理歸納。左邊Gen5(圖片左側) V.S. 右邊Gen6 (圖片右側)

Impedance Comparison

阻抗測試小結

單從阻抗上的表現,我們並沒有在Gen 5 和 Gen 6 間觀察到明顯的差異。但是在Connector Mating上,Gen 6 治具的阻抗反射Drop比Gen5治具要來得更小,具備更加穩定的特性。

Insertion Loss Comparison

插入損耗測試小結

從Insertion Loss@16GHz的表現上,我們可以直接發現Gen 6治具全面超越Gen5。

- 從CLB Tx + CBB Rx 的連接量測結果可發現,在16GHz的量測點上,有著 0.5495 dB差異。

- 從CLB Rx + CBB Tx 的連接量測結果可發現,在16GHz的量測點上,有著 0.8927 dB差異。

結語

即便PCI-SIG協會目前對外表示PCIe Gen5 的治具可以通用在 Gen6的測試上,不過我們仍然可以從實際量測的報告結果中看到,協會在新版的PCIe Gen 6治具上還是做了一定程度的進化和改良,再加上Gen6 在Loss Budget 上減少的情況下,未來若想要針對新一代PCIe Gen6 Compliance Electrical進行相關量測,使用全新的測試治具勢必是測試者需要特別考慮的,屆時百佳泰治具可以全然滿足大家的需求。

下一篇,百佳泰將以全新概念化的治具與協會治具來一場世紀對決。有興趣的你可千萬不要錯過!