PCI Express Gen5

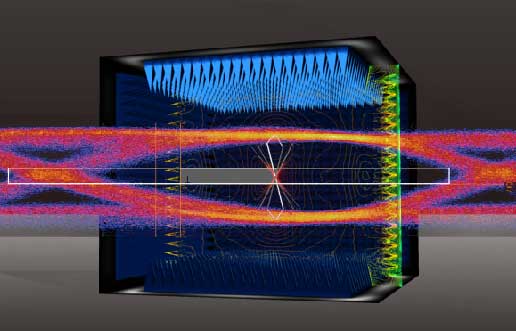

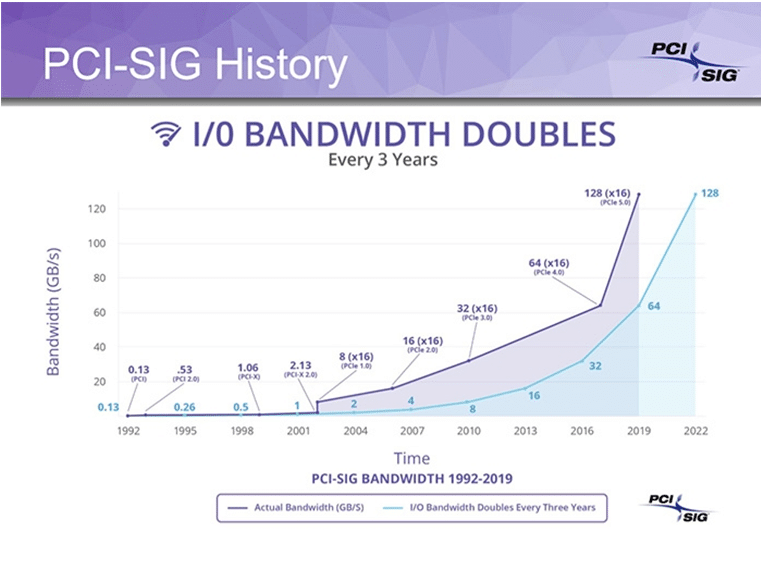

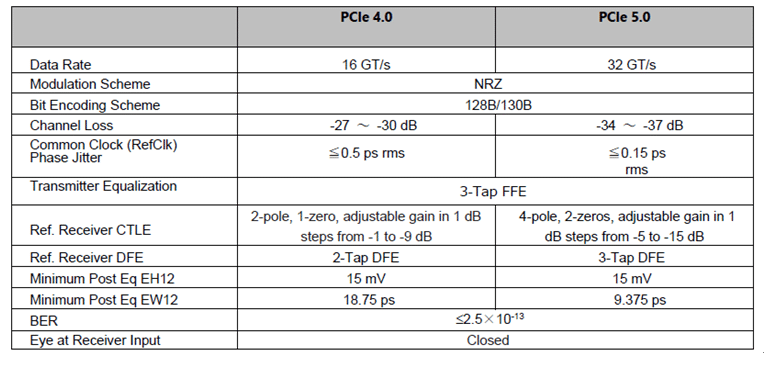

隨著PCI Express標準從第4代 (16.0 GT/s) 進化到第5代 (32.0 GT/s),其信號速率從PCIe 4.0的16GT/s提升到了32GT/s,PCIE 5.0依然使用128/130編碼方式,x16頻寬從64GB/s提升到了128GB/s。

PCIe 5.0和4.0有什麼差別?

除了頻寬翻倍之外,PCIe 5.0還帶來了其他變化,例如改變電氣設計以改善信號完整性,向後相容PCIe等等。此外,PCIe 5.0還設計了新標準,減少延遲,並降低長距離傳輸中的信號衰減。

PCIe 4.0和5.0具備許多共同點:兩者均使用 NRZ 調變、128B/130B 編碼,相同的 2.5×10-13 BER 目標以及相同的連接器腳位排列。發射器使用相同的 FFE 方式,並具有 11 組接頭預設 (P0-P10)。

相較於PCIe 4.0使用的2-pole、1-zero CTLE回應,PCIe 5.0使用4-pole、2-zero CTLE 濾波器回應。新的 CTLE 提供更大的彈性,以及從-5到-15 dB更深的增益範圍。PCIe 5.0還增加了第三個參考接收器(DFE)。

速率從16GT/s提升到32GT/s的最大困難,莫過於最大允許損耗從30dB增加到37dB;毫不意外的是,PCIe 5.0通道要求也一併歷經了重新定義,因此板卡機電 (CEM) 規格要求擴充卡只能採用表面黏著貼裝連接器。工程師也因為資料速率加倍而面對各種新的驗證挑戰:

- 克服更高的通道損耗及符號間干擾

- 設計能在更加受限的環境中,以較小邊際運作的組件及平臺

- 同時在實體層和通訊協定層進行除錯

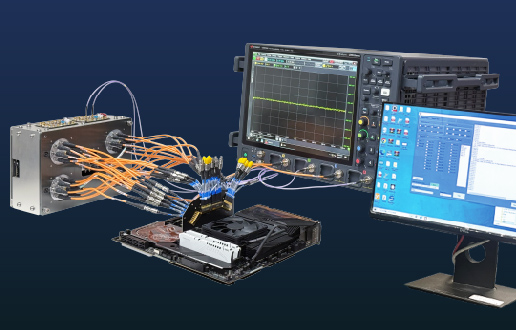

發送、接收端測試規範

發送端的測項包含:

- Tx Signal Quality Test

- Tx Preset Test

- Tx LEQ Test

- Tx Initial TXEQ Test

- Lane Margining Test

- PLL Test

- CLK Test

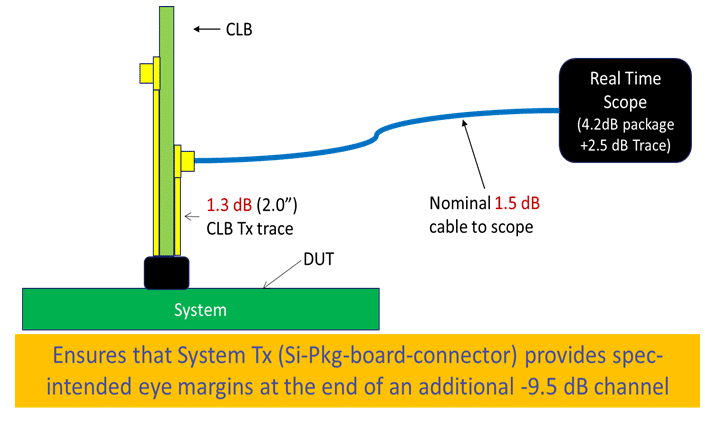

System Tx Diagrams

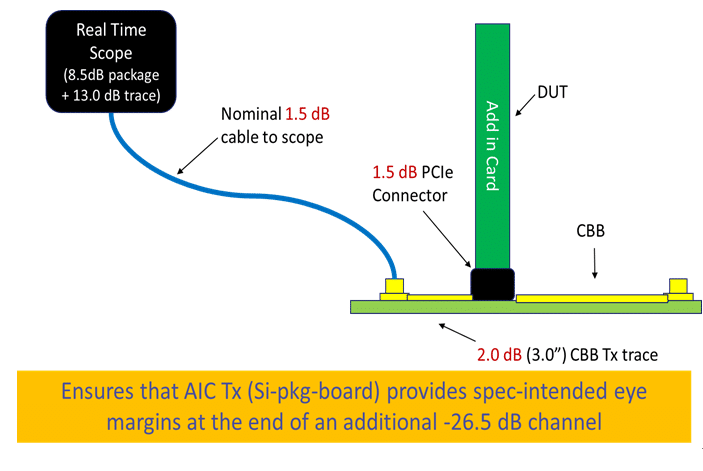

AIC Tx Diagrams

接收端的測項包含:

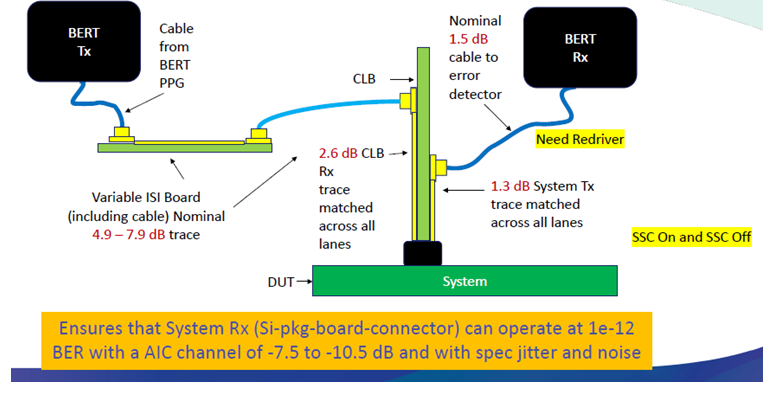

- RX BERT Test

- RX LEQ Test

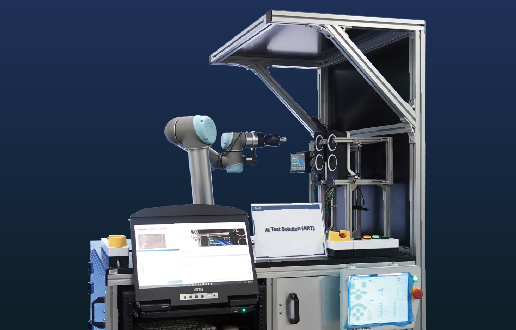

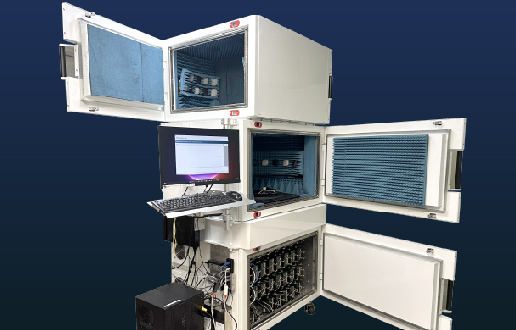

百佳泰依據PCI Express的測試程式提供與PCI-SIG Compliance Workshop一致的測試服務。我們擁有完整的測試設備和技術,並多次舉辦和參與PCIe插拔認證大會(Plugfest),可以為您的產品提供最及時的服務,並確保您產品的品質。請敬請期待百佳泰PCI Express 5.0的測試服務。