關於PCIe :

PCIe是一種高速的序列式匯流排介面,它能夠將電腦的主機板和各種擴充卡連接在一起,實現資料的傳輸和通訊。自2001年開始,Intel在IDF(Intel Developer Forum)上公布了3GIO(Third Generation I/O)的概念後,隔年正式定名為PCI Express,PCIe就正式走入PC界,成為了一種新的標準。

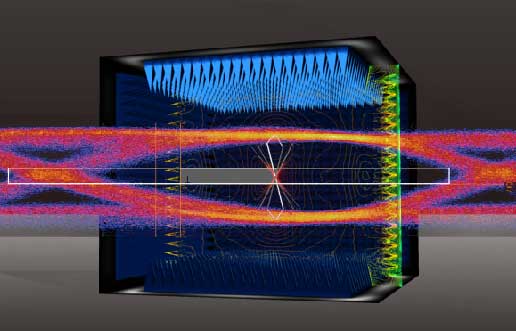

PCIe的高頻寬設計,讓它可以支援更多的應用和需求,從最初的Gen 1,每條線路傳輸速度僅2.5 GT/s(Giga Transfers per second),直至現在火紅的Gen 5,每條線路傳輸速度高達32.0 GT/s,提升了12.8倍之多,這對在不同應用層,如:Storage(儲存裝置)、VGA(視訊顯示卡)或是需要大資料傳輸進行運算的領域是相當受用的。然而在面對如此高速的PCIe Gen 5介面時,其驗證方式肯定是比以往的Gen 3/ 4世代更加嚴苛,而這部分,就是許多廠商難以跨越的門檻。

驗證內容與其導致的嚴重潛在風險

需驗證PCIe Gen5的產品首先要面對的包含以下三大項:

1. 搭配的治具板設計是否到位?

2. 是否依照協會PCIe-SIG PCIe Gen 5 規範進行設計?

3. 所設計出來的治具板是否能通過PCIe-SIG PCIe Gen 5 的測試標準?PCIe Gen 5規範在IL/RL/FEXT/NEXT這些S-Parameter上都有較之前Gen 3/ Gen 4嚴格的設定,為的就是避免使用者在PCIe Gen 5的裝置上使用時,有不愉快的體驗而設下標準,而這就是Allion開發PCIe Gen 5 Socket CEM board的初衷-前期就能夠協助客戶解決產品驗證的問題,進而提升產品的競爭力與市場佔有率。

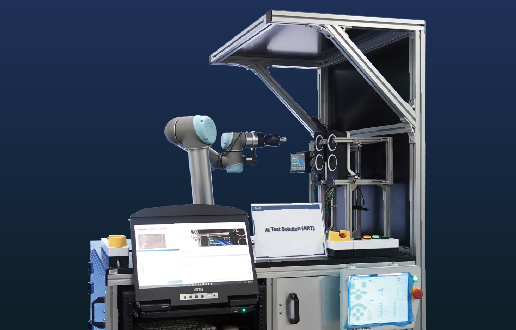

百佳泰提供完善的解決方案:

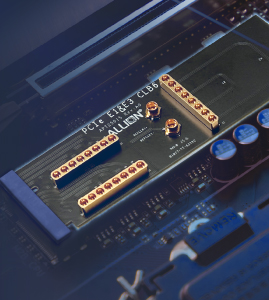

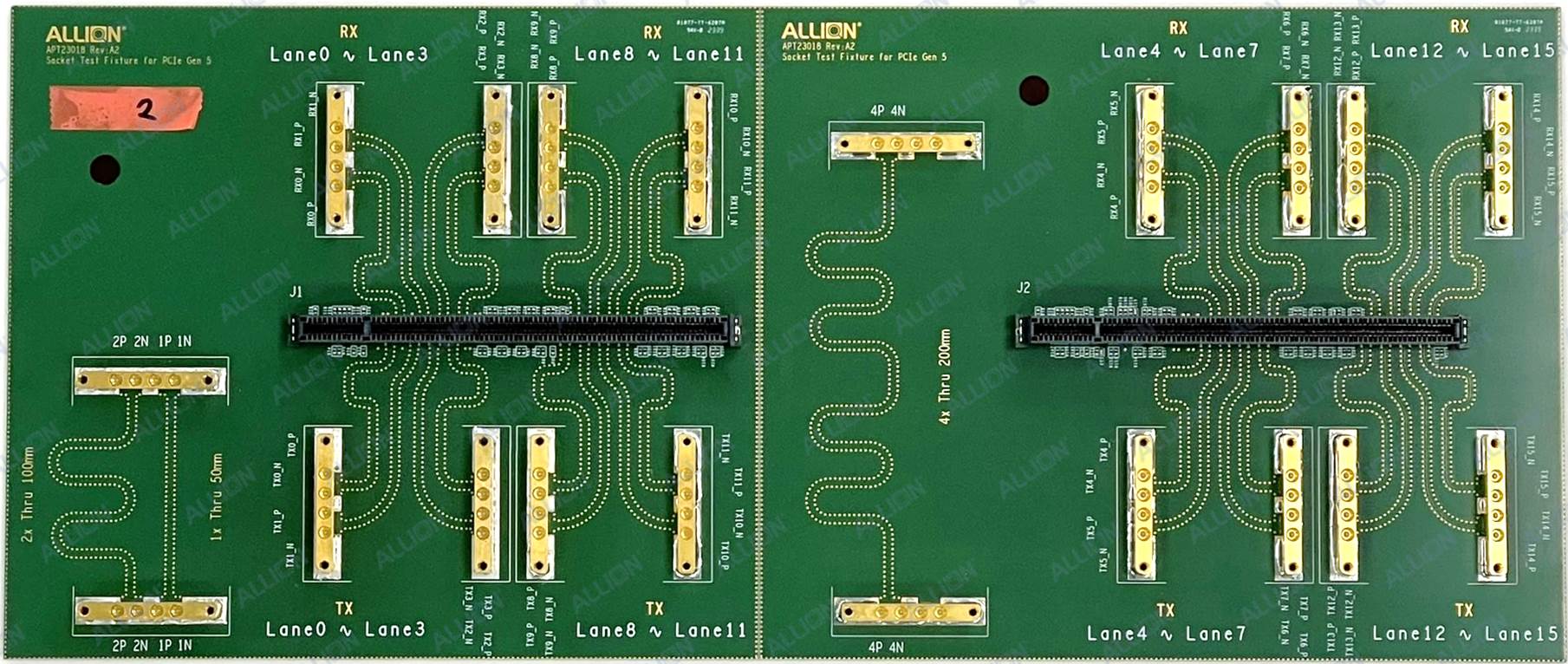

為了協助想開發PCIe Gen 5裝置的廠商對協會規範作驗證,Allion製作出PCIe 5.0 Socket的CEM board 來針對高頻的訊號作驗證,其特點是採用了SMPM連接器,除了方便及簡化連接測試用的SMA Cable外,也提供除了現在Cable驗證用的前4 lanes之外,剩餘12 條Lanes的測試環境,這對現在或未來有完整16條lanes測試需求的廠商來說是相當受用的。

下圖是Allion PCIe 5.0 Socket的CEM board:

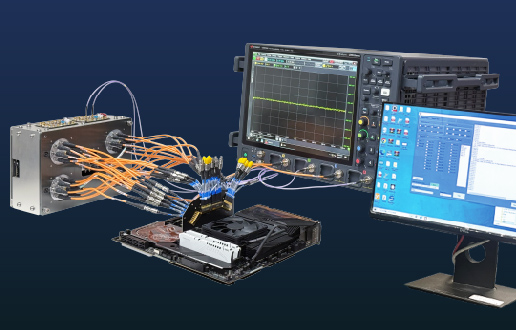

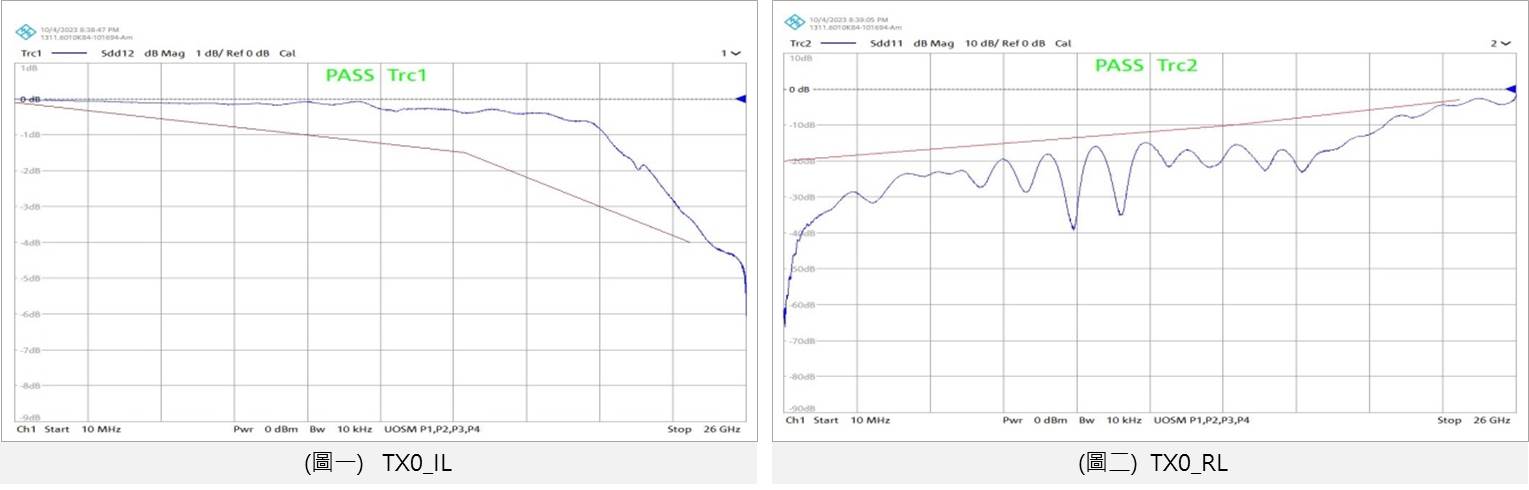

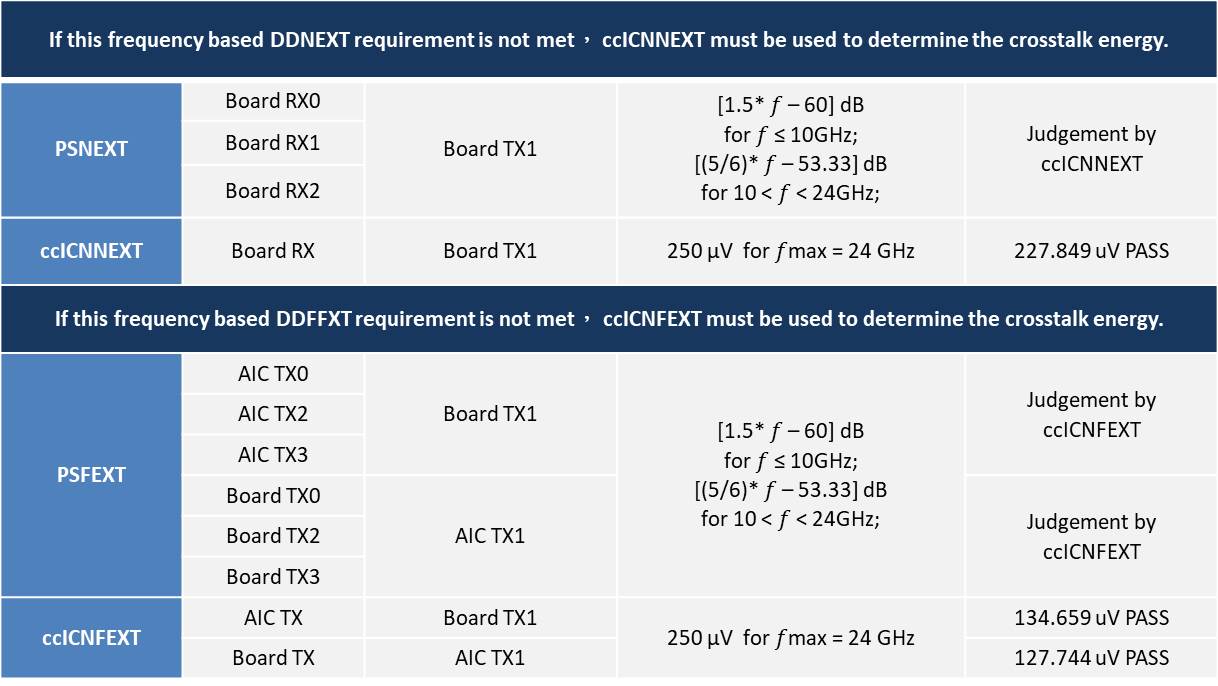

下圖一、二為實際量測Allion PCIe 5.0 Socket CEM board TX0的IL/RL的實際數據,以及整體NEXT/ FEXT的結果(僅供參考):

*AIC: Intel PCIe Gen 5 Add-in Card

百佳泰同時擁有高階的向量網路分析儀(Vector Network Analyzer),最高頻寬高達67GHz,能夠精準量測治具的高頻特性,呈現真實且準確的設計結果。

百佳泰在標準治具或客製化的治具設計有著以下的優勢:

Faster 更快速

百佳泰不僅擁有超過30年以上的專業實績、專業的技術團隊以及一應俱全的測試環境與高規格的儀器設備,在完成治具設計後能提供快速且正確的量測結果。

Easier 更便利

能提供一站式的治具設計及產品量測服務,與客戶一同為產品品質進行嚴格把關。

Better 更完善

百佳泰累積多年的豐富專案經驗及能力,有充足的量測經驗來解讀儀器的曲線含義,並提供解決方案的建議,幫助客戶解決問題以加速產品上市時間。

若您對於治具設計相關的顧問服務有進一步需求,歡迎透過線上表單與我們聯繫,百佳泰服務團隊將誠摯為您服務!